# Packaging- und Handling-Prüfungen nach ISO 10605: Wie vergleichbar sind Prüfungen mit unterschiedlichen ESD-Generatoren?

Prof. Dr.-Ing. Stephan Frei, cand. ing. Wei Wu, Dipl.-Ing. Ulf Hilger, TU Dortmund, Dortmund Dipl.-Ing. David Johnsson, Dr.-Ing. Matthias Stecher, Infineon AG, Neubiberg

#### Abstract

ESD-tests are often known to suffer from bad reproducibility. The most important reasons are often claimed to be the human factor and changing environmental conditions. Another important source of error is that transient fields that appear in system level testing are unspecified. For tests where only the discharge current is of importance and the discharge is made directly into a metallic surface the so called contact discharge mode can be used in order to increase reproducibility. This method is used for pin-testing in the Packaging and Handling test section according to ISO 10605. Due to missing field influence reproducibility should be high. However, differences in test results depending on the used generator have been reported. In this paper it will be investigated to what extent allowed variations within the standard can lead to different test results. Results from several test series on integrated circuits are presented to show how the used generator influences the results from Packaging and Handling tests. Differences in current shapes between the ESD-generators are also investigated and the failure modes in ICs are explained. The results are also valid for tests according to the IEC 61000-4-2 standard.

# Kurzfassung

ESD-Prüfungen gelten oft als schlecht reproduzierbar. Dies hat sehr unterschiedliche Gründe, meist werden der menschliche Faktor und wechselnde Umweltbedingungen als die Wichtigsten angeführt. Bei Systemprüfungen bilden auch die nicht genormten transienten Felder der ESD eine große Fehlerquelle. Wenn nur der Entladestrom eine Rolle spielt und die Entladung in eine metallische Oberfläche abgegeben werden kann, so ist es durch Verwendung des sogenannten Kontaktentlademodus des ESD-Generators möglich, die Reproduzierbarkeit zu erhöhen. Bei der Packaging- und Handling-Prüfung nach ISO 10605 nutzt man diese Option. Aufgrund des fehlenden Feldeinflusses sollte die Reproduzierbarkeit relativ hoch sein. Dennoch hört man immer wieder von unterschiedlichen Prüfergebnissen in Abhängigkeit von dem verwendeten Generatortyp. Inwieweit die durch die Normen erlaubten Toleranzen zu Abweichungen bei dem Prüfergebnis führen können, soll in diesem Beitrag geklärt werden. Der Beitrag stellt Ergebnisse aus Versuchsreihen an unterschiedlichen integrierten Schaltkreisen mit unterschiedlichen ESD-Generatoren vor. Es wird aufgezeigt, dass der Generatortyp maßgeblich ein Testergebnis bei einer Packaging- und Handlingprüfung beeinflussen kann. In Abhängigkeit von dem in der Prüfung verwendeten normenkonformen Generator kann eine um den Faktor 3 schwankende Ladespannung erforderlich sein, um den selben Fehler hervor zu rufen. Die vorgestellten Ergebnisse lassen sich auch auf Prüfungen nach IEC 61000-4-2 übertragen.

#### 1 Einleitung

Packaging- und Handling-Prüfungen am Ende des Entwicklungsprozesses eines Elektroniksystems sollen sicherstellen, dass die oft nicht vermeidbare ESD-Belastung in der Produktion und auch beim Kunden nicht zu Ausfällen führen kann. Leider wird immer wieder von einer schlechten Reproduzierbarkeit der ESD-Prüfungen berichtet. Im Extremfall kann eine bestandene Prüfung keine Sicherheit gegen Feldausfälle bieten.

Für die schlechte Reproduzierbarkeit von ESD-Prüfungen gibt es eine Reihe von Gründen. Neben dem menschlichen Faktor und den Umweltbedingungen spielt das statistische Verhalten des Lichtbogens eine große Rolle [1,2]. Durch die Einführung der Kontaktentladung in den wichtigsten Normen [3,4], bei der einige Eckwerte des Stroms klar definiert werden können, glaubt man seit einigen Jahren, dass zumindest ESD-Prüfungen auf metallische Testpunkte gut zu reproduzieren sind.

Das Problem der nicht genormten transienten Felder der ESD wird damit offensichtlich nicht gelöst und wurde in der Literatur vielfach diskutiert. Bei den transienten Feldern hängt das Störpotential neben der Stromform von dem mechanischen Aufbau des Generators und der Auswahl und Anordnung der passiven Elemente ab. Alle Normen lassen hier zu viele Freiheitsgrade. Im Rahmen eines großen

Round-Robin-Tests [5] wurde vor kurzem festgestellt, dass in Abhängigkeit von dem verwendeten ESD-Generatortyps die Generatorspannung um fast bis zu dem Faktor 4 schwanken kann, um an dem gleichen Prüfling einen Ausfall hervorzurufen. Diese Abweichungen sind dramatisch und legen aufgrund der sehr großen Schwankungsbreite der Ausfallspannung den Verdacht nahe, dass nicht nur die fehlende Festlegung der transienten Felder verantwortlich ist. Auch der Stromverlauf ist möglicherweise nicht hinreichend genau spezifiziert. Die erlaubten Toleranzen sind groß und der Widerstand einiger Anwender und Generatorhersteller hat in den letzten Jahren verhindert, dass diese kleiner werden konnten. Die derzeit verwendeten Kalibriereinrichtungen für den Strom sind zudem nicht in der Lage alle Details des Pulses ausreichend und reproduzierbar zu charakterisieren. Zur Zeit wird an einer neuen IEC-Norm gearbeitet, die sogar eine noch größere Schwankungsbreite des Stromverlaufs als heute zulassen soll.

Um den Einfluss des Stroms verschiedener kommerzieller IEC-Generatoren zu untersuchen, wurden Messungen der Stromformen vorgenommen und miteinander verglichen. Außerdem wurden notwendige Ladespannungen bestimmt, um an verschiedenen LIN-Transceivern, die als Prüflinge ausgewählt wurden, einen Ausfall hervorzurufen. LIN-Transceiver sind typische Kfz-Komponenten, die sich in vielen Steuergeräten finden lassen. Bei den geprüften Transceivern von Infineon handelt es sich um Entwicklungsmuster, die einen etwas komplexeren Ausfallmechanismus aufweisen. Die Ergebnisse werden im Folgenden vorgestellt und analysiert.

# 2 Packaging und Handling Prüfungen an Kfz-Elektroniken

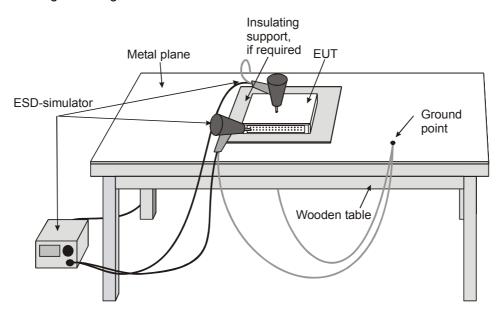

ESD-Prüfungen gegen Packaging- und Handling-Schäden werden in der ISO-Norm mit Hilfe eines Tischaufbaus durchgeführt. Der Aufbau ist in Abbildung 1 dargestellt. Der Generator wird in der Regel im Kontaktentlademodus betrieben. In Anlehnung an diesen Aufbau wurden auch die hier beschriebenen Untersuchungen durchgeführt.

Abbildung 1: Prüfaufbau nach ISO 10605 für Packaging und Handling Prüfungen

# 3 Mess- und Prüfaufbauten/ Prüflinge

#### 3.1 Mess- und Prüfaufbauten

Die Generatorströme wurden an einem konventionellen Strommessplatz gemessen. Ein Stromtarget nach [3] wurde hierfür verwendet. Gemessen wurde mit einen Digitaloszilloskop der Firma LeCroy mit einer Analogbandbreite von 2 GHz.

Für die Untersuchung der LIN-Transceiver wurde eine Testplatine entwickelt und gefertigt, auf der mit einem Sockel die Prüflinge befestigt werden können. Die Platine kann über einen Metallblock gut mit der horizontalen Koppelplatte verbunden werden. Ein gut zugänglicher Testpunkt, der direkt mit dem LIN-Pin des Transceivers verbunden ist, befindet sich auf der Platine. In Voruntersuchungen konnte gezeigt werden, dass der Sockel keinen nennenswerten Einfluss hat. Die Platine ist als eine Steuergerätenachbildung gedacht. Es ist davon auszugehen, dass das Verhalten der Transceiver in einem realen Gesamtsystem ähnlich sein wird.

Für der Untersuchung der LIN-Transceiver wurden 4 Generatoren von unterschiedlichen Herstellern mit verschiedenen Netzwerken von 150 pF/ 330  $\Omega$  oder 150 pF/ 2000  $\Omega$ , die einen Impulsverlauf nach DIN EN 61000-4-2 oder ISO 10605 erzeugen können, verwendet (Tabelle 1).

| Generator                                      | Netzwerke                                       |

|------------------------------------------------|-------------------------------------------------|

| NoiseKen TC-815R                               | 150 pF/ 330 $\Omega$ oder 150 pF/ 2000 $\Omega$ |

| Schaffner NSG 438                              | 150 pF/ 330 $\Omega$ oder 150 pF/ 2000 $\Omega$ |

| Schlöder SESD 30000                            | 150 pF/ 330 $\Omega$ oder 150 pF/ 2000 $\Omega$ |

| EM Test ESD 30, Kontaktentladung nur bis 10 kV | 150 pF/ 330 $\Omega$ oder 150 pF/ 2000 $\Omega$ |

Tabelle 1: Verwendete Generatoren mit unterschiedlichen Netzwerken

Abbildung 2: Testplatine auf der metallischen Halterung mit Masseverbindung

# 3.2 Prüflinge

Für die Untersuchung des Einflusses des ESD-Generators auf das Ausfallverhalten von Kfz-IC wurden 4 unterschiedliche Infineon LIN-Transceiver mit 8-14 Pins entwickelt, um das ESD Verhalten zu untersuchen.

| Transceiver | Beschreibung                                                       |

|-------------|--------------------------------------------------------------------|

| Α           | Kleiner DMOS, kleine ESD-Struktur, Standardfertigungsprozess       |

| В           | Wie A, aber andere DMOS-Gateansteuerung, Standardfertigungsprozess |

| С           | Wie B, aber besondere Prozessparameter in der Fertigung            |

| D           | DMOS ist vergrößert, größere ESD-Struktur                          |

**Tabelle 2: Untersuchte LIN-Transceiver**

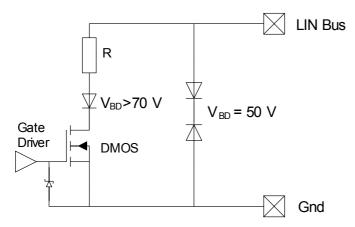

Ein vereinfachtes Schaltbild von dem Ausgangstreiber des LIN-Transceivers ist in der Abbildung 2 zu sehen. Hauptbestandteil ist ein DMOS Transistor, der bei einer Spannung von 70 Volt in den Durchbruch geht. Wenn diese Spannung überschritten wird, kann der Transistor maximal 1-2 Ampere zerstörungsfrei leiten und braucht deswegen eine zusätzliche Schutzstruktur, um ESD-Ströme abzuleiten.

Der ESD Schutz besteht aus Dioden mit einer Durchbruchspannung von 50 Volt. Somit besteht ein Abstand von 20 Volt zur Durchbruchspannung des DMOS Transistors. Die Dioden selbst haben eine ESD-Festigkeit von 10-17 kV (150 pF/ 330  $\Omega$ ), die mit deren Größe wächst. Im Gegensatz zu der Testvariante D haben die Muster A bis C eine halb so großen DMOS-Transistor und eine ESD-Struktur die zweidrittel so groß ist wie die von der Variante D. Die Varianten B und C haben identische Designs, wurden aber mit unterschiedlichen Prozessparametern gefertigt. Die Variante B wurde mit dem Standardprozess hergestellt. Die Variante A wurde ebenfalls mit dem Standardprozess hergestellt, unterschiedet sich aber von dem Design von B und C bezüglich der DMOS-Gateansteuerschaltung. Eine Übersicht zu den Unterschieden findet sich in Tabelle 2.

Abbildung 3: Vereinfachtes Schaltschema der Ausgangsstufe des LIN-Transceivers

## 3.3 Durchführung der Prüfungen

Vor einem ESD-Test wird zunächst die I/U-Kennlinie durch einen I/U-Schreiber aufgenommen. Dieser Verlauf dient später als Referenz, um über Abweichungen einen Fehler zu detektieren. Vor jeder Entladung auf den LIN-Pin werden die auf der ESD-Spitze gespeicherten Ladungen durch Berühren der Masse abgeleitet. Nach der Entladung werden mögliche Ladungen auf dem LIN-Pin über einen 1 M $\Omega$ -Widerstand nach Masse abgeleitet. Es folgt dann wieder eine Kennlininenmessung, die mit der Referenzkennlinie vergleichen wird. Wenn kein Fehler festgestellt werden kann, folgt die nächste Untersuchung mit einer höheren Ladespannung. Diese Prozedur wird solange wiederholt bis die I/U-Kurve ein verändertes Verhalten aufweist. Der Test wurde für jede IC-Variante mindestens drei Mal durchgeführt. Die wichtigsten Prüfparameter sind in Tabelle 3 aufgelistet.

| Definition           | Parameter                                       |

|----------------------|-------------------------------------------------|

| Typ der Entladung    | Kontaktentladung                                |

| Netzwerk             | 150 pF/ 330 $\Omega$ oder 150 pF/ 2000 $\Omega$ |

| Entladungsspannung   | 1 kV bis U <sub>Ausfall</sub> (max. 30 kV)      |

| Schrittweite         | 1 kV                                            |

| Polarität            | positiv/ negativ                                |

| Zahl der Entladungen | 3                                               |

| Wiederholungsrate    | 0,2 Hz                                          |

| Pin zum Testen       | LIN-Bus-Anschluss                               |

| Fehlererkennung      | Aufnahme und Vergleich der I/U-Kennlinien       |

Tabelle 3: Testdefinition und – Parameter der LIN-Transceiver

# 4 Ergebnisse

#### 4.1 Strommessungen

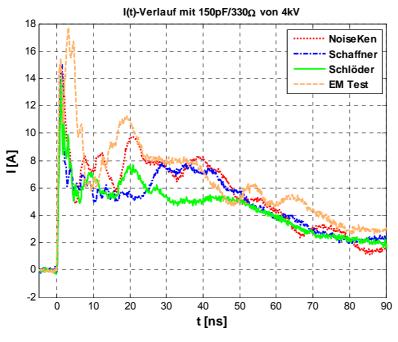

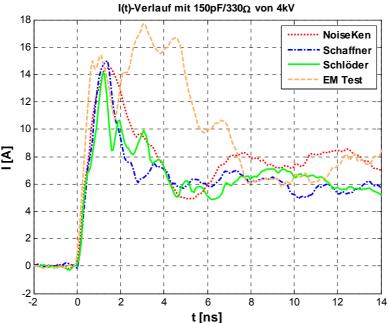

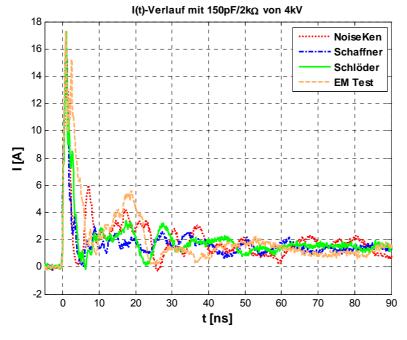

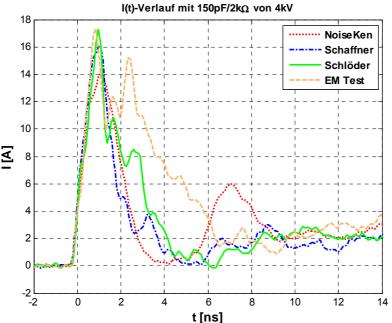

In Abbildung 4 bis Abbildung 7 sind die gemessenen Stromverläufe der verwendeten Generatoren mit verschiedenen Netzwerken bei einer Ladespannung von 4kV dargestellt. Bei der Strommessung der Generatoren mit dem Netzwerk 150 pF/ 330  $\Omega$  zeigte sich, dass die erste Stromspitze bei dem Schlöder-Generator am kleinsten und bei dem Schaffner-Generator am größten ist. Darüber hinaus fällt die erste Stromspitze bei der Strommessung mit dem Netzwerk 150 pF/ 2000  $\Omega$  bei dem NoiseKen-

Generator wesentlich kleiner als bei anderen Generatoren aus. Der Stromverlauf des EM Test-Generators ist aufgrund der Doppelspitze problematisch. In der Norm wird von einem einzelnen Puls ausgegangen. Dieser Puls ist über die Anstiegszeit und die Amplitude grob spezifiziert. Inwiefern ein zweiter Puls, der in der Amplitude den ersten Puls auch noch überragt, zulässig ist, kann nicht eindeutig geklärt werden. Die Norm spezifiziert heute ein Netzwerk, das nur den langsamen Anteil des ESD-Pulses formt. Der erste schnelle Puls wird im Wesentlichen durch den geometrischen Aufbau bestimmt, dieser ist leider nicht festgelegt.

Abbildung 4: Gemessene Stromkurven mit 150 pF/ 330  $\Omega$  Entladenetzwerk, 0 bis 90 ns

Abbildung 5: Gemessene Strom-kurven mit 150 pF/  $330~\Omega$  Entladenetzwerk, 0 bis 14 ns

Abbildung 6: Gemessene Stromkurven mit 150 pF/ 2000  $\Omega$  Entladenetzwerk, 0 bis 90 ns

Abbildung 7: Gemessene Stromkurven mit 150 pF/ 2000  $\Omega$  Entladenetzwerk, 0 bis 14 ns

# 4.2 Bestimmung der Ausfallspannung für verschiedene LIN-Transceiver

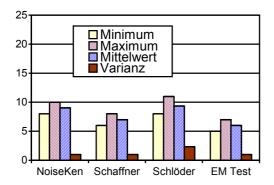

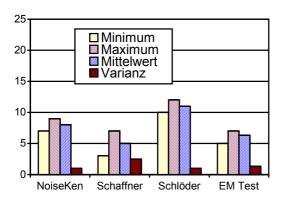

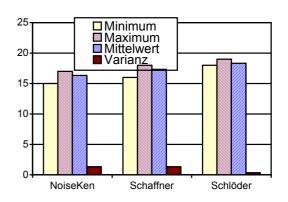

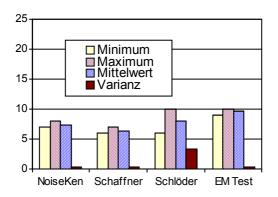

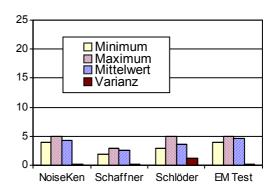

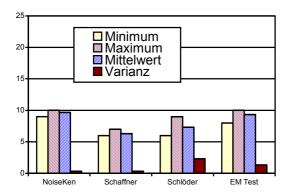

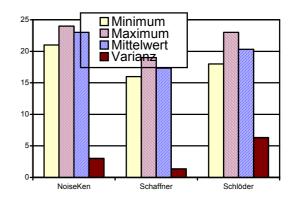

Die Abbildungen 8 bis 15 zeigen die gemessenen Ausfallspannungen der verschiedenen Testobjekte in Abhängigkeit von dem ESD-Generator und dem Entladenetzwerk. Die gezeigten Messungen wurden an der TU-Dortmund mit dem vorher beschriebenen Aufbau durchgeführt. Auch Infineon hatte bei internen Untersuchungen vorher unterschiedliche ESD-Festigkeiten in Abhängigkeit von dem ESD-Generator beobachtet. In allen Abbildungen sind das Maximum, das Minimum, der daraus resultierende Mittelwert und die Varianz dargestellt.

Minimum

Maximum

Mittelwert

Varianz

NoiseKen Schaffner Schlöder EM Test

Abbildung 8: Ausfallsspannungen für LIN-Transceiver A (150 pF/ 330  $\Omega$ -Netzwerk)

Abbildung 9: Ausfallsspannungen für LIN-Transceiver B (150 pF/ 330  $\Omega$ -Netzwerk)

Abbildung 10: Ausfallsspannungen für LIN-Transceiver C mit (150 pF/ 330  $\Omega$ -Netzwerk)

Abbildung 11: Ausfallsspannungen für LIN-Transceiver D (150 pF/ 330  $\Omega$ -Netzwerk)

Abbildung 12: Ausfallsspannungen für LIN-Transceiver A (150 pF/ 2000  $\Omega$  Netzwerk)

Abbildung 13: Ausfallsspannungen für LIN-Transceiver B (150 pF/ 2000  $\Omega$  Netzwerk)

Abbildung 14: Ausfallsspannungen für LIN- Abbildung 15: Ausfallsspannungen für LIN-Transceiver C (150 pF/ 2000  $\Omega$  Netzwerk)

Transceiver D (150 pF/ 2000  $\Omega$  Netzwerk)

#### 5 Analyse der LIN-Ausfälle

#### Ausfallanalyse

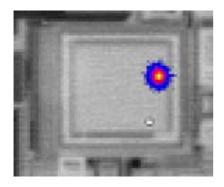

Die Fehleranalysen an den ausgefallenen LIN Transceivern (Varianten A bis C) haben stets gezeigt, dass der DMOS Transistor zerstört wurde (Abbildung 16). Die ESD Strukturen waren immer noch voll funktionsfähig. Im Falle von der Variante D wurde stets die ESD-Struktur zerstört. Der DMOS wurde beim Typ D nie beschädigt. Prozessvariationen konnten die ESD-Festigkeit der Variante D nicht mindern. Mittels TIM [6] konnte für langsame Pulse mit einer Anstiegszeit von 30 ns nachgewiesen werden, dass stets die ESD-Struktur den Puls ableitete. Sie wurde aber selbst oft mit 8 A Pulsen nicht zerstört. Im Falle des IEC-ESD-Pulses ist die Anstiegszeit des ersten Pulses um mindestens den Faktor 20 größer. Damit wird der DMOS-Transistor über seine Miller-Kapazität aufgesteuert, was dazu führt, dass der DMOS den ersten Teil des GUN-Impulses zum Teil übernimmt. Wenn der DMOS nicht groß genug dimensioniert ist, wird dieser zerstört. Dieses erklärt die besseren Ergebnisse der Variante D, die ja im Vergleich zu den anderen Varianten einen doppelt so großen DMOS aufweist. Die Gateansteuerschaltung der Variante A ist so konzipiert, dass der DMOS Transistor homogener im Vergleich zur Designvariante B/C einschaltet. Somit wird die vom DMOS übernommene ESD-Energie gleichmäßiger über dessen Fläche verteilt. Dieses erklärt die zur Variante B leicht bessere ESD Festigkeit. Die ESD-Unterschiede zwischen B und C verdeutlichen, dass sehr große Prozessabweichungen zu stark unterschiedlichen ESD-Festigkeiten führen können. Aber wie hier nicht gezeigte Untersuchungen an D bewiesen haben, muss dieses nicht grundsätzlich in stark unterschiedlichen ESD-Festigkeiten resultieren, wenn das Design entsprechend robust ist.

Abbildung 16: Fehleranalyse an einem ausgefallenen Transceiver zeigt einen Schaden im DMOS mit deutlich erhöhtem Leckstrom

Dass die steile Impulsnadel des IEC-Pulses für den DMOS Ausfall verantwortlich ist, konnte über die Untersuchungen mit dem Entladenetzwerk 150 pF/ 2000  $\Omega$  bestätigt werden. Im Falle dieses Netzwerkes wird der energiehaltige Teil des ESD-Pulses stark unterdrückt. Da dieser Pulsteil fast nicht mehr auftritt, ergeben sich für die Varianten A bis C, die ja ähnliche DMOS-Strukturen aufweisen, ähnliche ESD-Festigkeiten unabhängig vom Entladenetzwerk. Im Falle der Variante D ergibt sich eine ähnliche Festigkeit mit beiden Netzwerken.

Die Hypothese, dass der erste Teil des GUN-Pulses den DMOS gefährdet, wurde bei Infineon auch mittels eines Hoch-Enerigie Pulsers, der sehr kurze aber hohe Strompulse generiert, verifiziert. Diese Pulse führten zu ähnlichen DMOS-Ausfällen aber nie zu ESD-Schutzstrukturausfällen.

Um die These noch weiter zu verifizieren, wurde die ESD-Festigkeit mit negativen ESD-Impulsen bestimmt. Bei dieser Belastung wird der DMOS in Durchlassrichtung betrieben. Weil ferner die Diode in seinem Leitungspfad eine Durchbruchspannung jenseits von 70V hat, fließt bei dieser Belastung fast der ganze ESD-Strom durch die antiserielle ESD-Struktur. Somit sollte die negative Gun-ESD-Festigkeit von der antiseriellen ESD-Struktur bestimmt sein. Die Messungen an allen 4 Varianten bestätigten diese Schlussfolgerung. Sie ergaben in allen Fällen Werte jenseits von 10kV mit sehr geringen Streuungen.

#### 6 Diskussion

Aus den Ergebnissen kann gefolgert werden, dass unabhängig vom verwendeten ESD-Generator und dem Versuchsaufbau die DMOS Ansteuerung (Variante A) und die DMOS-Größe (Variante D) die größten Einflussfaktoren sind, um die ESD-Festigkeit einzustellen. Die DMOS Größe ist dabei sicherlich die effektivste Designmöglichkeit.

Nichtsdestotrotz zeigen die Untersuchungen, dass den belasteten Bauteilen keine eindeutige ESD-Festigkeit zugeordnet werden kann, denn zum einen liefert jeder Generator für sich selbst eine zu große Streuung und zum anderen weichen die gemessenen ESD-Festigkeiten zwischen den Generatoren sehr stark voneinander ab. Diese Abweichungen sind nur unwesentlich auf Prozessschwankungen oder das Design zurückzuführen, denn innerhalb jeder Variante waren die ESD-Ergebnisse zu unterschiedlich. Die Messungen an der TU-Dortmund haben Abweichung bei den Mittelwerten um den Faktor 3 zwischen den Generatoren nachweisen können. Betrachtet man die Minimal und Maximalwerte, sind Abweichungen um den Faktor 7 möglich. D.h. dass im Extremfall mit einem normenkonformen Generator eine Ausfallspannung von 1 kV und mit einem anderen auch normenkonformen Generator eine Ausfallspannung von 7 kV festgestellt werden kann. Diese Varianz ist definitiv zu groß. Der wesentliche Grund für diese inakzeptable Abweichung sind die unterschiedlichen Stromverläufe der Generatoren. Die gemessenen Abweichungen sind sehr groß, die Norm lässt zu viele Freiheitsgrade. Nur die Anstiegszeit und die Amplitude des ersten Pulses sind spezifiziert. Da offensichtlich die tolerierten Abweichungen der Pulse schon zu einem signifikant unterschiedlichen Schädigungsverhalten und somit unterschiedlichen ESD-Festigkeiten führen, kann nur gefolgert werden, dass die zur Zeit gültige Normung ungeeignet ist, moderne Elektronikstrukturen reproduzierbar zu testen.

Weiterhin geschieht der Normierungsnachweis auf Basis eines einzigen Lastfalles, der zudem noch niederohmig ist. Es ist somit vorstellbar, dass bei hochohmigeren Lasten wie den LIN-Transceivern die Strom-Zeit-Verläufe noch größere Unterschiede aufweisen. Um eineindeutige ESD-Festigkeitsaussagen mit unterschiedlichen Generatoren machen zu können, müssen die ISO- und die IEC-ESD-Normen so bald wie möglich maßgeblich geändert werden.

# **Danksagung**

Die Arbeiten zu dieser Veröffentlichung wurde durch das Bundesministerium für Bildung und Forschung, im Rahmen des Förderprogramms IKT2020 und des Projekts SPOT-2, Förderkennzeichen 01M3180, MEDEA+ 2T205 unterstützt.

#### Literatur

- [1] D. Pommerenke, ESD: transient fields, arc simulation and rise time limit, Journal of Electrostatics, 36, 1995

- [2] S. Frei, M. Senghaas, R. Jobava, W. Kalkner, The Influence of Speed of Approach and Humidity on the Intensity of ESD, International Zurich Symposium on Electromagnetic Compatibility, 1999

- [3] IEC 61000-4-2 ed. 2 CD: Electromagnetic Compatibility (EM) Part 4: Testing and measurement techniques Section 2: Electrostatic discharge immunity test, 2007

- [4] ISO 10605 CDV for 2<sup>nd</sup> ed.: Road vehicles Electrical disturbances from electrostatic discharges

- [5] M. Hirata, T. Takahashi, N. Schibuya, Evaluation of Falling Time Restriction of ESD Immunity Test Current Waveform: The Result of IEC 61000-4-2 Round Robin Test in Japan, IEEE International Symposium on EMC, 2007

- [6] D. Pogany, Single-Shot thermal energy mapping of semiconductor devices with the nanosecond resolution using holographic interferometry, IEEE EDL, 2002